Build a Reference Design#

The Vitis AI provides the reference design, called the X+ML Reference Design, where “X” refers to hardware-accelerated pre-processing tasks, and “Machine Learning” refers to the inference task running on the Neural Processing Unit (NPU). The reference design demonstrates an end-to-end Machine Learning solution, encompassing the entire process from inputting image or video files to generating and storing Machine Learning output.

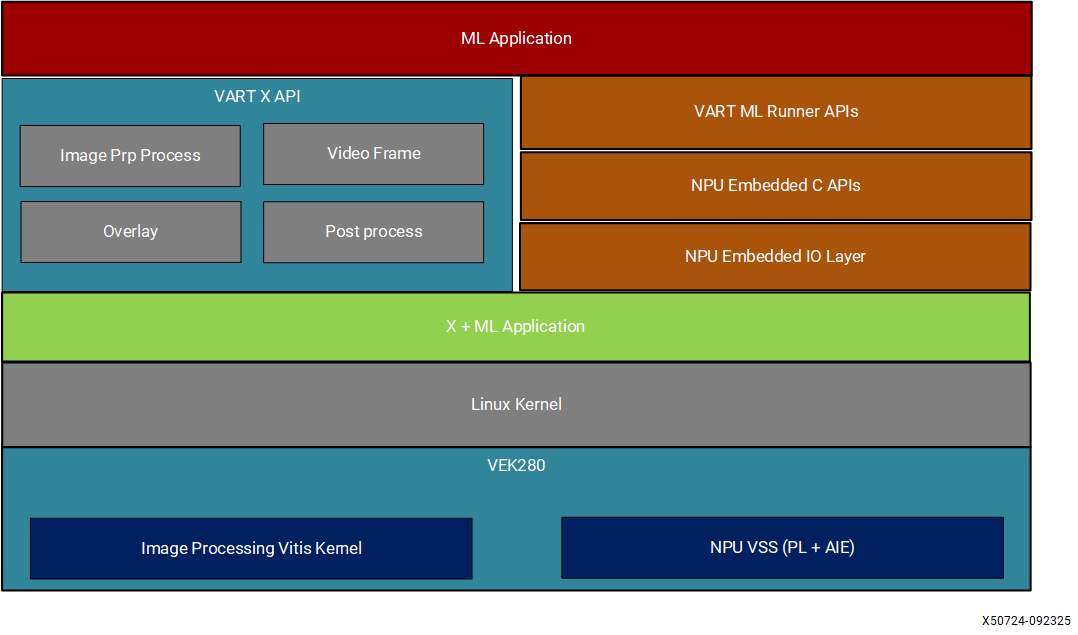

The following figure illustrates the architecture of the X+ML reference design, developed using the VART APIs.

Supported Features#

Implements hardware pre-processing using Image Processing PL kernel (including resizing, color space conversion, normalization, and cropping).

Performs inference using the kernelized NPU IP.

Provides software post-processing for ResNet50 model.

Includes functionality for drawing bounding boxes and text corresponding to the inference results on the input image.

Build a Reference Design#

The Vitis AI release package contains both prebuilt binaries and the sources to generate them. The prebuilt binaries include the SD card image, NPU software applications, and X+ML application. You can verify these prebuilt binaries on target hardware, as covered in the Execute Sample Model. Additionally, you have the option to regenerate the binaries from the provided sources. The following steps outline the procedure:

Prerequisites#

Download Vitis AI source code (vitis-ai-2025.1.tar) from the lounge

VEK280 BSP v2025.1: Download VEK280 BSP v2025.1.

Obtain License for NPU IP: You need to obtain the license for NPU IP. Without the license, you receive a synthesis error while building the reference design. Refer to Obtaining License for NPU IP for more details.

Download and Extract Sources#

Follow these steps to download and extract the sources:

Download the source (vitis-ai-2025.1.tar) from the lounge

Download the BSP file

cd <path-to-downloaded-vitis-ai-2025.1.tar>

tar xf vitis-ai-2025.1.tar

cd Vitis-AI

Choose the right NPU IP for setting. Refer to the snapshot generation message for your model. The message shows you which NPU IP is chosen for snapshot generation. You need to use the same NPU IP to build the reference design:

# By default, the VE2802_NPU_IP_O00_A304_M3_INT8 (high performance NPU IP) is chosen to generate snapshot and building the reference design. source npu_ip/settings.sh

Note

The previous command downloads the NPU IP and NPU software packages.

export

PATH=$PATH:/usr/sbin

Source Required Tools#

source <path-to-installed-Petalinux-v2025.1>/settings.sh

source <path-to-installed-Vitis-v2025.1>/settings64.sh

Build Reference Design Binaries#

This step performs the following actions:

Download Docker to create snapshots.

Download the pre-compiled Neural Processing Unit Intellectual Property (Neural Processing Unit IP).

Create the Vitis platform using the provided Docker container sources.

Run the Vitis tool to link all hardware accelerator kernels (pre-processing, inferencing, post-processing).

Create an SD card image file (example: VE2802_NPU_IP_O00_A304_M3_INT8_sd_card.img).

# Untar the downloaded package using tar -xvf vitis-ai-2025.1.tar

# export HOME_DIR=<UNTARRED DOWNLOADED PACKAGE PATH>

$ export HOME_DIR=<path-to-extracted-vitis-ai-2025.1.tar>/Vitis-AI/

$ cd $HOME_DIR

$ bash

$ export ENABLE_FREQ_ADJUST=FALSE

$ export DISABLE_YOLOX_TAIL_PL=FALSE

$ cd examples/reference_design/vek280/

$ make all BSP_PATH=<BSP file Path>

Example: make all BSP_PATH=<downloaded-bsp-path>/xilinx-vek280-xsct-v2025.1-05221048.bsp

# The released 2025.1 VEK280 BSP should be downloaded from the below path to point to BSP_PATH

# https://www.xilinx.com/member/forms/download/xef.html?filename=xilinx-vek280-xsct-v2025.1-05221048.bsp

Note

The default value for

ENABLE_FREQ_ADJUSTis false. If you configure"export ENABLE_FREQ_ADJUST=True", the Vitis design uses postlink scripts to adjust frequencies to avoid timing violations in the design. By defaultENABLE_FREQ_ADJUSTdisables the freqency adjustments from the post link scripts.If

DISABLE_YOLOX_TAIL_PL=false, yolovx_tail is enabled in the Vitis design (and becomes the default). If you setDISABLE_YOLOX_TAIL_PL=true, the yolox_tail kernel is not integrated with the Vitis design.

The SD card image is generated after following the previous steps. You can refer to the Execute Sample Model for instructions on flashing the SD card and running the steps.